# **Bt481A**

# 110 MHz 256-Word Color Palette 15-, 16-, and 24-Bit True Color Power-Down RAMDAC

Designed specifically for high-performance color graphics, the Bt481A RAM-DAC supports three true-color modes: 15-bit (5:5:5, 32 K colors) TARGA format, 16-bit (5:6:5, 65 K colors) XGA format, and 24-bit BGR (8:8:8, RGB/BGR, 16.8 M colors) true-color format. It also supports 8-bit pseudo-color format (256 colors).

The Bt481A has a 256 x 18 (24) lookup table RAM, 15 x 8 (24) overlay registers, and triple 8-bit D/A converters. Both 6- and 8-bit color modes are supported.

A power-down mode is available on the Bt481A to reduce power requirements when the analog outputs are not used. This is useful in laptop computer systems that require the option to drive an external RGB monitor.

The Bt481A has on-chip analog output comparators to simplify diagnostics and debugging, with the result output onto the SENSE\* pin. Also included is an on-chip voltage reference to simplify use of the device.

The Bt481A generates RS-343-compatible video signals into a doubly terminated load.

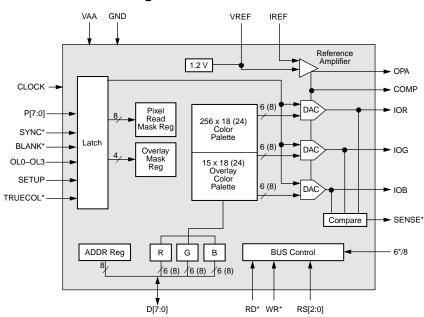

### **Functional Block Diagram**

### **Distinguishing Features**

- 110 MHz Operation

- Supports 8:8:8, 24-bit true color and VGA overlay

- Supports 8:8:8 24-bit RGB/BGR selectable true-color format

- Supports 5:6:5 XGA true-color format

- Supports 5:5:5 TARGA true-color format

- Replaces Bt471/475/476/477/478 which are pin compatible

- Power-on reset for internal registers

- · Power-down mode

- Antisparkle circuitry

- Analog output conparators

- Triple 6-bit (8-bit) D/A converters

- 256 x 18 (24) color palette RAM

- 15 x 18 (24) overlay registers

- Optional internal voltage reference

- · Programmable pedestal

- Sync on all three channels

- Standard MPU interface

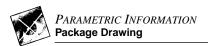

- 44-pin PLCC package

#### **Applications**

- · High-resolution color graphics

- CAE/CAD/CAM

- Image processing

- Instrumentation

- Desktop publishing

- Laptop computers

Brooktree Corporation • Rockwell Semiconductor Systems, Inc. • 9868 Scranton Road • San Diego, CA 92121-3707 619-452-7580 • 1-800-2-BT-APPS • FAX: 619-452-1249 • Internet: apps@brooktree.com • L481A\_C

### **Ordering Information**

|   | Model Number                                                                                              | Color<br>Palette RAM | Overlay<br>Palette | Speed   | Package               | Ambient<br>Temperature Range |  |  |  |

|---|-----------------------------------------------------------------------------------------------------------|----------------------|--------------------|---------|-----------------------|------------------------------|--|--|--|

|   | Bt481AKPJ110                                                                                              | 256 x 24             | 15 x 24            | 110 MHz | 44-Pin Plastic J-Lead | 0° to +70° C                 |  |  |  |

| Ī | Note: The Bt481AKPJ110 replaces the following products: Bt471, Bt475, Bt476, Bt477, Bt478, Bt481/482/483. |                      |                    |         |                       |                              |  |  |  |

Copyright © 1996 Brooktree Corporation. All rights reserved.

Print date: November 1996

Brooktree reserves the right to make changes to its products or specifications to improve performance, reliability, or manufacturability. Information furnished by Brooktree Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Brooktree Corporation for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by its implication or otherwise under any patent or patent rights of Brooktree Corporation.

Brooktree products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Brooktree product can reasonably be expected to result in personal injury or death. Brooktree customers using or selling Brooktree products for use in such applications do so at their own risk and agree to fully indemnify Brooktree for any damages resulting from such improper use or sale.

Brooktree is a registered trademark of Brooktree Corporation. Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

Specifications are subject to change without notice.

PRINTED IN THE UNITED STATES OF AMERICA

# TABLE OF CONTENTS

| List of Figures                                  | . V  |

|--------------------------------------------------|------|

| List of Tables                                   | . vi |

| Functional Description                           | . 1  |

| Pin Information and Block Diagram                | . 1  |

| MPU Interface                                    | . 5  |

| Writing Color Palette RAM Data                   | . 6  |

| Reading Color Palette RAM Data                   | . 6  |

| Writing Overlay                                  |      |

| Reading Overlay                                  |      |

| 15, 16, and 24/32 Bits-per-Pixel Operation.      |      |

| 15, 16, and 24 Bits-per-Pixel Dual-Edge Clock    |      |

| Additional Information                           |      |

| Accessing Command Registers                      |      |

| Accessing Command Register B                     |      |

| Accessing Command Registers Without The RS2 Line |      |

| Automatic Detection Without The RS2 Line         | 10   |

| 6-Bit/8-Bit Color Selection                      |      |

| Power-Down Mode                                  | 11   |

| SENSE* Output                                    | 12   |

| Internal VREF and DAC Output Level               | 13   |

| Controller Interface                             | 14   |

| Internal Registers                               | 19   |

| Command Register A                               | 19   |

| Command Register B                               | 20   |

| PC Board L  | ayout Considerations           | 21 |

|-------------|--------------------------------|----|

|             | Component Placement            | 21 |

|             | Power and Ground Planes        | 22 |

|             | Device Decoupling              | 22 |

|             | Power Supply Decoupling        | 22 |

|             | COMP Decoupling                | 26 |

|             | VREF Decoupling                | 26 |

|             | Digital Signal Interconnect    | 26 |

|             | Analog Signal Interconnect     | 26 |

|             | Analog Output Protection       | 27 |

| Application | Information                    | 29 |

|             | Using Multiple Devices         | 29 |

|             | ESD and Latchup Considerations | 29 |

|             | Reference Selection            | 29 |

|             | Sleep Operation                | 29 |

|             | Initializing the Bt481A        | 30 |

| Parametric  | Information                    | 33 |

| DC Ele      | ectrical Parameters            | 33 |

| AC Ele      | ectrical Parameters            | 36 |

| Timing      | g Waveforms                    | 38 |

| Packa       | ge Drawing                     | 14 |

| Revisi      | on History                     | 45 |

### **List of Figures**

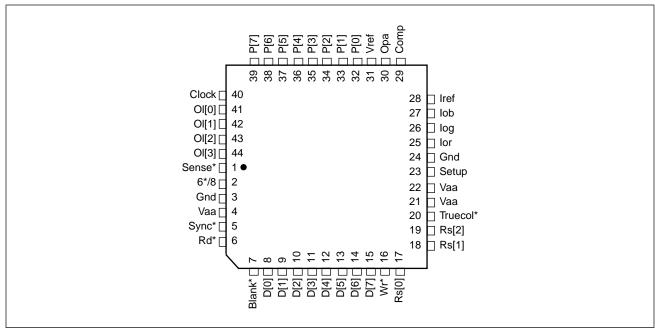

| Figure 1.  | Pinout Diagram                                                         | . 3 |

|------------|------------------------------------------------------------------------|-----|

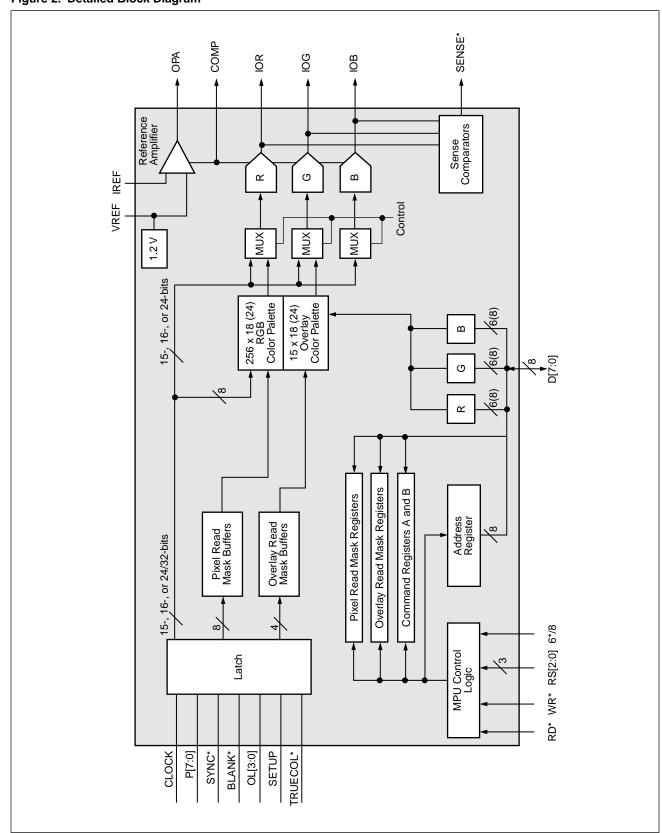

| Figure 2.  | Detailed Block Diagram                                                 |     |

| Figure 3.  | Bt481A Internal VREF and DAC Output                                    | 13  |

| Figure 4.  | RS-343A Composite Video Output Waveforms (SETUP = 7.5 IRE)             | 15  |

| Figure 5.  | RS-343A Composite Video Output Waveforms (SETUP = 0 IRE)               | 16  |

| Figure 6.  | PS/2 Composite Video Output Waveforms (SETUP = 0 IRE)                  | 17  |

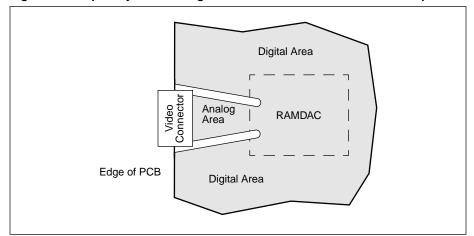

| Figure 7.  | Sample Layout Showing Power and Ground Plane Isolation Gaps            | 22  |

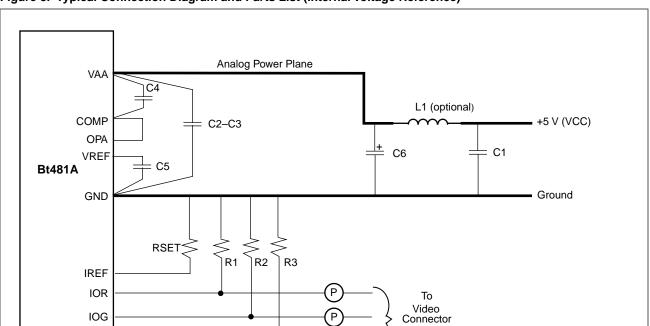

| Figure 8.  | Typical Connection Diagram and Parts List (Internal Voltage Reference) | 23  |

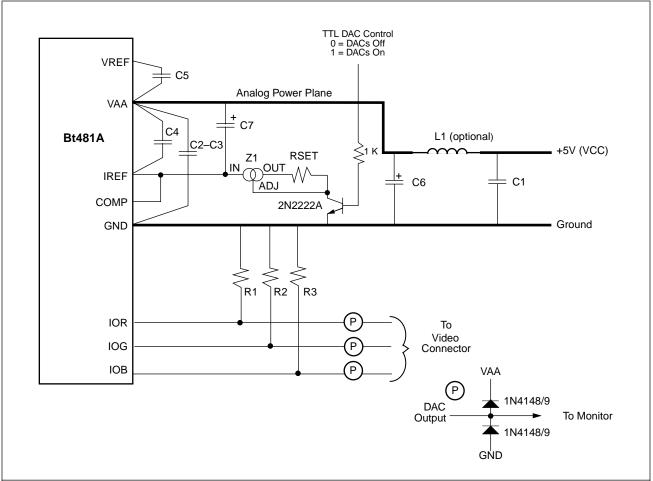

| Figure 9.  | Typical Connection Diagram and Parts List (External Voltage Reference) | 24  |

| Figure 10. | Typical Connection Diagram and Parts List (External Current Reference) | 25  |

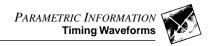

| Figure 11. | MPU Read/Write Timing                                                  | 38  |

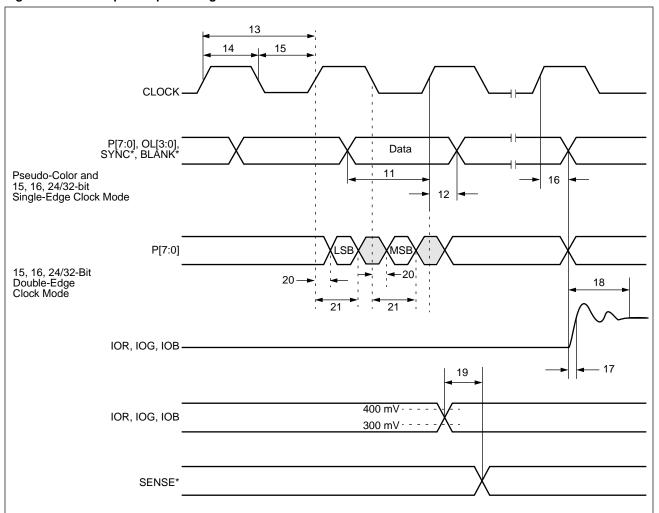

| Figure 12. | Video Input/Output Timing                                              | 39  |

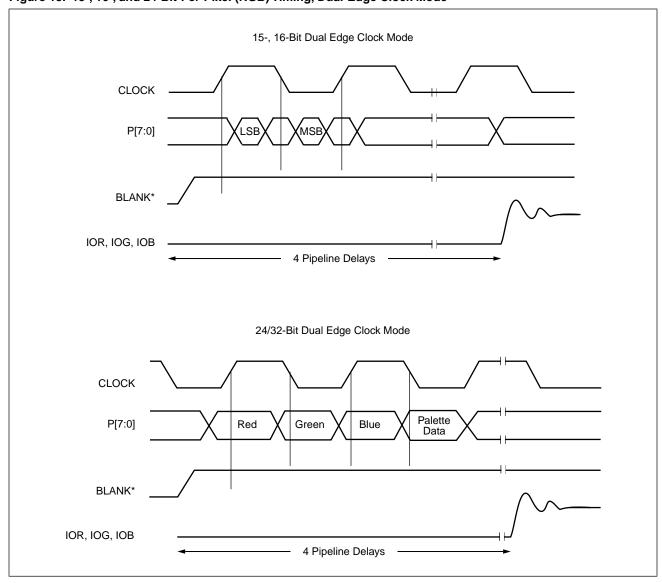

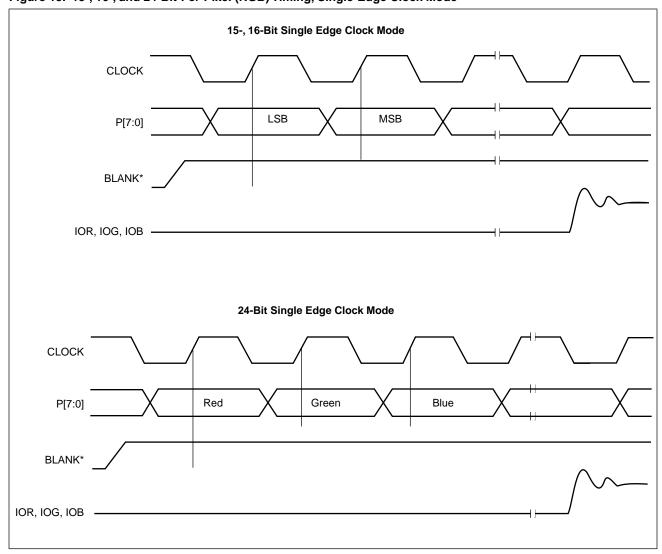

| Figure 13. | 15-, 16-, and 24-Bit-Per-Pixel (RGB) Timing, Dual-Edge Clock Mode      | 40  |

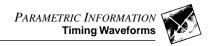

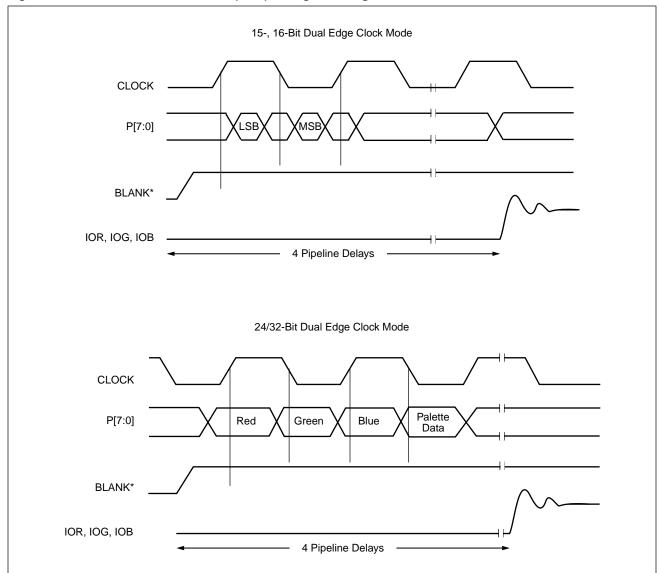

| Figure 14. | 15-, 16-, and 32-Bit-Per-Pixel (BGR) Timing, Dual-Edge Clock Mode      | 41  |

| Figure 15. | 15-, 16-, and 24-Bit-Per-Pixel (RGB) Timing, Single-Edge Clock Mode    | 42  |

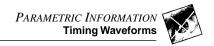

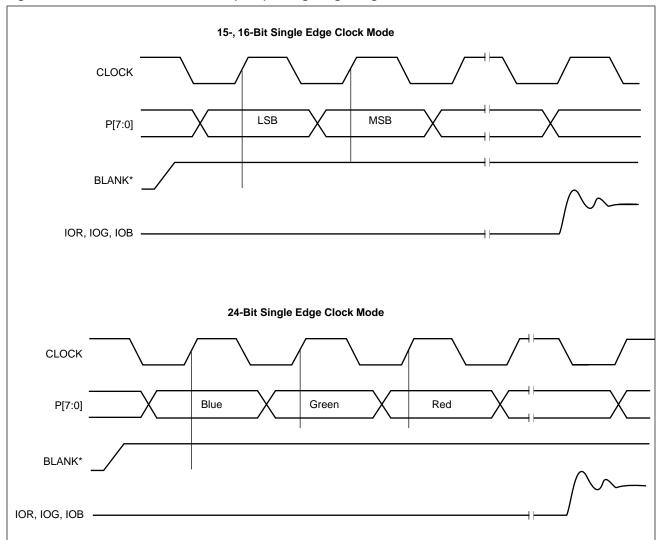

| Figure 16. | 15-, 16-, and 24-Bit-Per-Pixel (BGR) Timing, Single-Edge Clock Mode    | 43  |

| Figure 17. | 44-Pin Plastic J-Lead (PLCC)                                           | 44  |

### **List of Tables**

| Table 1.  | Pin Descriptions                                                        | 1    |

|-----------|-------------------------------------------------------------------------|------|

| Table 2.  | Control Input Truth Table                                               | 5    |

| Table 3.  | Address Register (ADDR) Operation                                       | 5    |

| Table 4.  | Word Assignments to DACs                                                | 7    |

| Table 5.  | Indirect Register Addressing Truth Table                                | 9    |

| Table 6.  | Pixel and Overlay Control Truth Table (Pixel Read Mask Register = \$FF) | . 14 |

| Table 7.  | RS-343A Video Output Truth Table (SETUP = 7.5 IRE)                      | . 15 |

| Table 8.  | RS-343A Video Output Truth Table (SETUP = 0 IRE)                        | . 16 |

| Table 9.  | PS/2 Video Output Truth Table (SETUP = 0 IRE)                           | . 17 |

| Table 10. | Recommended Operating Conditions                                        | . 33 |

| Table 11. | Absolute Maximum Ratings                                                | . 33 |

| Table 12. | DC Characteristics                                                      | . 34 |

| Table 13. | AC Characteristics                                                      | . 36 |

### Pin Information and Block Diagram

Table 1 details the Bt481A's pin numbers, names, and descriptions. Figure 1 illustrates the pinout. Figure 2 is a detailed block diagram of the Bt481A.

Table 1. Pin Descriptions (1 of 3)

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | BLANK*   | Composite Blank Control Input (TTL compatible). A logic zero drives the analog outputs to the blanking level, as specified in Tables 7–9. BLANK* is latched on the rising edge of CLOCK. When BLANK* is a logical zero, the pixel and overlay inputs are ignored.                                                                                                                                                                                      |

| 23         | SETUP    | Setup Control Input (TTL compatible). This input is used to specify either a 0 IRE (logical zero) or 7.5 IRE (logical one) blanking pedestal. This pin should not be left floating                                                                                                                                                                                                                                                                     |

| 5          | SYNC*    | Composite Sync Control Input (TTL compatible). A logical zero on this input switches off a 40 IRE current source on the analog outputs (see Figures 8–10). SYNC* does not override any other control or data input, as shown in Tables 7–9; therefore, it should be asserted only during the blanking interval. It is latched on the rising edge of CLOCK. If sync information is not required on the video outputs, SYNC* should be connected to GND. |

| 40         | CLOCK    | Clock Input (TTL compatible). The rising edge of CLOCK latches the P[7:0], OL[3:0], SYNC*, and BLANK* inputs. It is typically the pixel clock rate of the video system. It is recommended that CLOCK be driven by a dedicated TTL buffer to avoid reflection-induced jitter.                                                                                                                                                                           |

| 32–39      | P[7:0]   | Pixel Select Inputs (TTL compatible). These inputs specify, on a pixel basis, which one of the 256 entries in the color palette RAM is to be used to provide color information. They are latched on the rising edge of CLOCK. P[0] is the LSB. Unused inputs should be connected to GND.                                                                                                                                                               |

| 41–44      | OL[3:0]  | Overlay Select Inputs (TTL compatible). These inputs specify which palette is to be used to provide color information, as specified in Table 6. When the overlay palette is accessed, the P[7:0] inputs are ignored. They are latched on the rising edge of CLOCK. OL[0] is the LSB. Unused inputs should be connected to GND.                                                                                                                         |

Table 1. Pin Descriptions (2 of 3)

| Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                              |          |               |                                                                                                       |                                     |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|-------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | COMP             | Compensation Pin. If an external or internal voltage reference is used, this pin should be connected to the reference amplifier output (OPA pin). If an external current reference is used, this pin should be connected to full-scale adjust control (IREF pin). A 0.1 μF ceramic capacitor must always be used to bypass this pin to VAA. The COMP capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum. The PC Board Layout Considerations section contains critical layout information.                                                                                        |                                                                                                                                                                                                                                                                              |          |               |                                                                                                       |                                     |  |  |

| 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VREF             | Voltage Reference Input. If an external voltage reference is used, it must supply this input with a 1.235 V (typical) reference. If an external current reference is used, this pin should be left floating, except for the bypass capacitor. A 0.1 µF ceramic capacitor should decouple this input to GND. The decoupling capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum. When using the internal reference, this pin should not drive any external circuitry other than the decoupling capacitor. The PC Board Layout Considerations section contains further information. |                                                                                                                                                                                                                                                                              |          |               |                                                                                                       |                                     |  |  |

| 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OPA              | must be o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Reference Amplifier Output. If an external or internal voltage reference is used, this pin must be connected to COMP. When an external current reference is used, this pin should be left floating. The PC Board Layout Considerations section contains further information. |          |               |                                                                                                       |                                     |  |  |

| 25–27                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IOR, IOG,<br>IOB | Red, Green, And Blue Current Outputs. These high-impedance current sources can directly drive a doubly-terminated 75 $\Omega$ coaxial cable. The PC Board Layout Considerations section contains further information.                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                              |          |               |                                                                                                       |                                     |  |  |

| IREF  Full-Scale Adjust Control. The IRE relationships in Figure regardless of the full-scale output current. When an externation ence is used, a resistor (RSET) connected between this nitude of the full-scale video signal. The relationship betwoutput current on each output is: $RSET (Ω) = K * 1,000 * VREF (V) / K  is defined in the table below. It is recommended that a for doubly-terminated 75 Ω loads (i.e., RS-343A application), a 182 Ω RSET resistor.$ |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                              |          |               | or internal voltage and GND controls in RSET and the fact (mA)  7 Ω RSET resistors). For PS/2 applies | e refer-<br>s the mag-<br>ull-scale |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Mode                                                                                                                                                                                                                                                                         | Pedestal | K (with sync) | K (no sync)                                                                                           |                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-bit                                                                                                                                                                                                                                                                        | 7.5 IRE  | 3.17          | 2.26                                                                                                  |                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-bit                                                                                                                                                                                                                                                                        | 7.5 IRE  | 3.195         | 2.28                                                                                                  |                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-bit                                                                                                                                                                                                                                                                        | 0 IRE    | 3.0           | 2.10                                                                                                  |                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-bit                                                                                                                                                                                                                                                                        | 0 IRE    | 3.028         | 2.12                                                                                                  |                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  | See the F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | See the PC Board Layout Considerations section for further information.                                                                                                                                                                                                      |          |               |                                                                                                       |                                     |  |  |

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | WR*              | Write Control Input (TTL compatible). D[7:0] data is latched on the rising edge of WR*, and RS[2:0] are latched on the falling edge of WR* during MPU write operations. RD* and WR* should not be asserted simultaneously.                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                              |          |               |                                                                                                       |                                     |  |  |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RD*              | Read Control Input (TTL compatible). To read data from the device, RD* must be a logical zero. RS[2:0] are latched on the falling edge of RD* during MPU read operations. RD* and WR* should not be asserted simultaneously.                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                              |          |               |                                                                                                       |                                     |  |  |

Table 1. Pin Descriptions (3 of 3)

| Pin Number Pin Name |          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17–19               | RS[2:0]  | Register Select Inputs (TTL compatible). RS[2:0] specify the type of read or write operation being performed, as detailed in Tables 2 and 3.                                                                                                                                                                                                                                                                                                                                                                                         |

| 8–15                | D[7:0]   | Data Bus (TTL compatible). Data is transferred into and out of the device over this 8-bit bidirectional data bus. D0 is the least significant bit.                                                                                                                                                                                                                                                                                                                                                                                   |

| 2                   | 6*/8     | 6-Bit/8-Bit Select Input (TTL compatible). This pin specifies whether the MPU is reading and writing 8 bits (logical one) or 6 bits (logical zero) of color information each cycle. For 8-bit operation, MPU Bit D[7] is the most significant bit during read/write cycles. For 6-bit operation, MPU bit D[5] is the most significant bit during read/write cycles. (D[7] and D[6] are ignored during write cycles and are logical zero during read cycles.)                                                                         |

| 1                   | SENSE*   | Sense Output (CMOS compatible). SENSE* is a logical zero if one or more of the IOR, IOG, and IOB outputs have exceeded the internal voltage reference level. SENSE* may not be stable while SYNC* is toggling. The SENSE* output can drive only one CMOS load.                                                                                                                                                                                                                                                                       |

| 20                  | TRUECOL* | True-Color Mode Select Input (TTL compatible). This signal is inverted and logically ORed with bit A[7] in Command Register A. A logical zero will enable the true-color modes. By programming the proper command register bits, the user can choose either 5:5:5, 5:6:5, 8:8:8, or 8:8:8:OL and determine whether the pixels are input on a single clock edge or a dual clock edge (see the Command Register section for details). The TRUECOL* pin should be tied to VAA to disable the hardware selection of the true-color mode. |

| 4, 21, 22           | VAA      | Analog Power. All VAA pins must be connected together on the same PCB plane to prevent latchup.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3, 24               | GND      | Analog Ground. All GND pins must be connected together on the same PCB plane to prevent latchup.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Figure 1. Pinout Diagram

Brooktree° L481A\_C 3

Figure 2. Detailed Block Diagram

### **MPU Interface**

As illustrated in the detailed block diagram (Figure 2), the Bt481A supports a standard MPU bus interface, allowing the MPU direct access to the color palette RAM and overlay color registers.

The RS[2:0] select inputs specify whether the MPU is accessing the address register, color palette RAM, overlay registers, or read mask register, as shown in Table 2. The 8-bit address register addresses the color palette RAM and overlay registers, eliminating the requirement for external address multiplexers. ADDR0 corresponds to D[0] and is the least significant bit (see Table 3).

**Table 2. Control Input Truth Table**

| RS[2] | RS[1] | RS[0] | Addressed by MPU                      |

|-------|-------|-------|---------------------------------------|

| 0     | 0     | 0     | Address Register (Palette Write Mode) |

| 0     | 1     | 1     | Address Register (Palette Read Mode)  |

| 0     | 0     | 1     | Color Palette RAM                     |

| 0     | 1     | 0     | Pixel Read Mask Register              |

| 1     | 0     | 0     | Address Register (Overlay Write Mode) |

| 1     | 1     | 1     | Address Register (Overlay Read Mode)  |

| 1     | 0     | 1     | Overlay Registers                     |

| 1     | 1     | 0     | Command Register A                    |

Table 3. Address Register (ADDR) Operation

|                           | Value                                                 | RS[2]            | RS[1]            | RS[0]            | Addressed by MPU                                                          |

|---------------------------|-------------------------------------------------------|------------------|------------------|------------------|---------------------------------------------------------------------------|

| ADDRa, (Counts Modulo 3)  | 00<br>01<br>10                                        |                  |                  |                  | Red Value<br>Green Value<br>Blue Value                                    |

| ADDR[7:0] (Counts Binary) | \$00–\$FF<br>0000 0000<br>0000 0001<br>:<br>0000 1111 | 0<br>1<br>1<br>: | 0<br>0<br>0<br>: | 1<br>1<br>1<br>: | Color Palette RAM<br>Reserved<br>Overlay Color 1<br>:<br>Overlay Color 15 |

# Writing Color Palette RAM Data

To write color data, the MPU writes the address register (RAM write mode) with the address of the color palette RAM location to be modified. The MPU performs three successive write cycles (6 or 8 bits each of red, green, and blue), using RS[2:0] to select the color palette RAM. After the blue write cycle, the 3 bytes of color information are concatenated into an 18-bit or 24-bit word and written to the location specified by the address register. The address register then increments to the next location, which the MPU may modify by writing another sequence of red, green, and blue data. A block of color values in consecutive locations may be written to by writing the start address and performing continuous RGB write cycles until the entire block has been written.

# Reading Color Palette RAM Data

To read color palette RAM data, the MPU loads the address register (RAM read mode) with the address of the color palette RAM location to be read. The contents of the color palette RAM at the specified address are copied into the RGB registers, and the address register is incremented to the next RAM location. The MPU performs three successive read cycles (6 or 8 bits each of red, green, and blue), using RS[2:0] to select the color palette RAM. Following the blue read cycle, the contents of the color palette RAM at the address specified by the address register are copied into the RGB registers and the address register again increments. A block of color values in consecutive locations may be read by writing the start address and performing continuous RGB read cycles until the entire block has been read.

#### **Writing Overlay**

To write overlay data, the MPU writes the address register (overlay write mode) with the address of the overlay location to be modified. The MPU performs three successive write cycles (6 or 8 bits each of red, green, and blue), using RS[2:0] to select the overlay registers. After the blue write cycle, the 3 bytes of color information are concatenated into an 18-bit or 24-bit word and written to the overlay location specified by the address register. The address register then increments to the next location, which the MPU may modify by writing another sequence of red, green, and blue data. A block of color values in consecutive locations may be written to by writing the start address and performing continuous RGB write cycles until the entire block has been written.

#### **Reading Overlay**

To read overlay data, the MPU loads the address register (overlay read mode) with the address of the overlay location to be read. The contents of the overlay register at the specified address are copied into the RGB registers, and the address register is incremented to the next overlay location. The MPU performs three successive read cycles (6 or 8 bits each of red, green, and blue), using RS[2:0] to select the overlay registers. Following the blue read cycle, the contents of the overlay location at the address specified by the address register are copied into the RGB registers and the address register again increments. A block of color values in consecutive locations may be read by writing the start address and performing continuous RGB read cycles until the entire block has been read.

### 15, 16, and 24/32 Bits-per-Pixel Operation

When the 15, 16, or 24/32 bits-per-pixel modes are activated (see Command Register A in the Internal Registers section), the inputs accept 16, 24, or 32 bits of pixel information from the 8-pin pixel port P[7:0]. The 8-bit inputs form a 16- or 24-bit pixel (B15–0/B23–B0) to directly drive the 8-bit triple video DACs. The color lookup table and the read mask register are bypassed. Internally, the unused LSBs of all DACs are forced to zero in 15 or 16 bits-per-pixel modes. The 16- and 24-bit word (B15–0/B23–B0) is assigned to the DACs according to Table 4.

Table 4. Word Assignments to DACs

| 8:8:8:8<br>True Color<br>Format RGB | 8:8:8:8<br>True Color<br>Format BGR | 5:6:5<br>XGA Format | 5:5:5<br>TARGA<br>Format | Comments             |

|-------------------------------------|-------------------------------------|---------------------|--------------------------|----------------------|

|                                     |                                     |                     | B15                      | Ignored              |

| B7-B0                               | B23-B16                             | B15-B11             | B14-B10                  | Red DAC              |

| B15-B8                              | B15-B8                              | B10-B5              | B9-B5                    | Green DAC            |

| B23-B16                             | B7-B0                               | B4-B0               | B4-B0                    | Blue DAC             |

| B31-B24                             | B31-B24                             |                     |                          | Palette or<br>Masked |

15, 16, and 24 Bits-per-Pixel Dual-Edge Clock In the 15 and 16 bits-per-pixel dual-edge clock mode (see the Command Register A, bits A[7:4] description in the Internal Registers section), the least significant byte is latched on the rising edge of the pixel clock when BLANK\* high is latched. Also in this mode, the most significant byte is latched on the falling edge of the pixel clock when BLANK\* high is latched. Therefore, only one input clock period is required to load a 16-bit pixel.

In the 32 bits-per-pixel dual-edge clock mode, 32 bits of data, 24 bits of true-color and 8 bits of palette index are latched on two rising and two falling edges. Therefore, only two input clock cycles are required to load a 32-bit pixel. If palette indexing is not required, logical zeros can be written for the palette overlay data, as location zero in the palette RAM cannot be accessed in this mode. Or palette overlay data can be masked out through the pixel read mask register. If the palette index data is not a logical zero or masked, the data will address any one of 255 locations in the palette RAM. Palette data has priority over bypass data.

### 15, 16, and 24 Bits-per-Pixel Single-Edge Clock

In the 15 and 16 bits-per-pixel single-edge clock mode (see Command Register A in the Internal Registers section), the inputs accept 16 bits of information by using two input clock cycles. The least significant byte is latched on the first rising edge of the input clock, and the most significant byte is latched on the second rising edge of the input clock. The bytes are synchronized with the BLANK\* signal. The first byte latched after BLANK\* goes high is the least significant byte. Since a pixel is latched in two clock cycles, the input clock must be twice as fast as the internal pipeline clock. The Bt481A has an internal divider to generate the pipeline clock from the input clock.

In the 24 bits-per-pixel single-edge clock mode, the inputs accept 24 bits of pixel data by using three input clock cycles. The red byte is latched on the first rising edge of the pixel clock when BLANK\* high is latched. The next two clock cycles latch the green and blue bytes. Since a 24-bit pixel is latched in three input clock cycles, the input clock must be three times as fast as the internal pipeline clock. The Bt481A has an internal divider to generate the pipeline clock from the pixel input clock. Palette data has priority over bypass data.

#### **Additional Information**

When the MPU is accessing the color palette RAM, the address register resets to \$00 following a blue read or write cycle to RAM location \$FF. While the MPU is accessing the overlay color registers, the 4 most significant bits of the address register (ADDR[7:4]) are ignored.

The MPU interface operates asynchronously to the pixel clock. Data transfers between the color palette RAM/overlay registers and the color registers (R, G, and B in the block diagram) are synchronized by internal logic. Data transfers take place in the period between MPU accesses. To reduce noticeable sparkling on the CRT during MPU access to the color palette RAMs, internal logic maintains the previous output color data on the analog outputs while the transfer between lookup table RAMs and the RGB registers occurs.

To keep track of the red, green, and blue read/write cycles, the address register has 2 additional bits (ADDRa and ADDRb) that count modulo three, as shown in Table 3. They are reset to zero when the MPU writes to the address register and are not reset to zero when the MPU reads the address register. The MPU does not have access to these bits. The other 8 bits of the address register, incremented following a blue read or write cycle (ADDR[7:0]), are accessible to the MPU. These bits are used to address color palette RAM locations and overlay registers. The MPU may read the address register at any time without modifying its contents or the existing read/write mode. The pixel clock must be active for MPU accesses to the color palette RAM.

### **Accessing Command Registers**

# Accessing Command Register B

Command Register B is defined to select SETUP, 6-bit/8-bit, and the sleep modes of Bt481A. There are only three register select lines and all eight combinations have already been used. Therefore, Command Register B must be accessed indirectly through Pixel Read Mode Register. Bit A0 of Command Register A must be set to a logical one to enable access to extended registers.

For example, Command Register B can be accessed with the following sequence of operations:

- 1 Set RS[2:0] = 110 to access Command Register A.

- 2 Write a logical one to Command Register A, bit A[0].

- 3 Set RS[2:0] = 000 for address register write mode.

- 4 Write address register to 0000 0010 for Command Register B.

- 5 Set RS[2:0] = 010 for pixel read mask register.

- 6 Read or write Command Register B.

- 7 Set RS[2:0] = 110 to access Command Register A.

- 8 Reset Command Register A, bit A[0] to a logical zero.

Table 5 contains specifications to indirectly address other registers.

Table 5. Indirect Register Addressing Truth Table

|                          | Value     | RS[2] | RS[1] | RS[0] | Bit A[0] | Registers             |

|--------------------------|-----------|-------|-------|-------|----------|-----------------------|

| ADDR 0-7 (counts binary) | 0000 0000 | 0     | 1     | 0     | 1        | Read Mask Register    |

|                          | 0000 0001 | 0     | 1     | 0     | 1        | Overlay Mask Register |

|                          | 0000 0010 | 0     | 1     | 0     | 1        | Command Register B    |

### Accessing Command Registers Without The RS2 Line

When the overlay functionality of the Bt481A is not used and the Register Select Line 2 (RS2) must be tied low at all times, the command registers of the Bt481A can still be accessed.

A flag will be set when the pixel read mask register (RS[1] = 1 and RS[0] = 0) is read four times consecutively. The next write to the pixel read mask register will be directed to Command Register A and can be used to set the bits in that register. Any access of the command register thereafter will also require four consecutive reads to the pixel read mask register. A write to any address other than the pixel read mask register will reset the flag.

If bit A2 in Command Register A is set to logical one, internally, the RS2 signal will also be set to logical one, even if the RS[2] pin is grounded. If bit A2 in Command Register A is set to logical zero, the state of the RS2 signal will depend on the logic state of the RS[2] pin.

# Automatic Detection Without The RS2 Line

In some applications it is necessary to detect the presence of Bt481A. This may be automated with a software routine accessing Command Register B. Bt481A's Command Register B has a unique signature which identifies its presence in the graphics system. The Pixel Read Mask Register and Command Register A must be used in order to gain access to Command Register B.

The required steps for the Bt481A auto-detect routine are listed below in the IPF protocol. These steps assume that RS2 line is grounded and is therefore not available.

| • | О | 3c6 | FF | Initialize Pixel Read Mask Register to FF.                                                                        |

|---|---|-----|----|-------------------------------------------------------------------------------------------------------------------|

| į | i | 3c6 |    | Read Pixel Read Mask Register 4 times consecu-                                                                    |

| į | i | 3c6 |    | tively, so that the next write will be directed to                                                                |

| į | i | 3c6 |    | Command Register A.                                                                                               |

| į | i | 3c6 |    |                                                                                                                   |

| • | 0 | 3c6 | 01 | Write a logical 1 to A0 so that the extended register set can be accessed.                                        |

| • | 0 | 3c8 | 02 | Set RS1–0 to 00 (address register write mode) and write address register to 0000 0010 (Command Register B).       |

| j | i | 3c6 |    | Set RS1–0 to 10 (read mask register) and read Command Register B). This should return a value of 1Eh.             |

| • | 0 | 3c8 | 00 | Set RS1–0 to 00 (address register write mode) and write address register to 0000 0000 (Pixel Read Mask Register). |

| • | 0 | 3c6 | FF | Restore Pixel Read Mask Register to FF.                                                                           |

| j | i | 3c6 |    | Read Pixel Read Mask Register 4 times consecu-                                                                    |

| j | i | 3c6 |    | tively, so that the next write will be directed to                                                                |

| j | i | 3c6 |    | Command Register A.                                                                                               |

| j | i | 3c6 |    | -                                                                                                                 |

| , | О | 3c6 | 00 | Write a logical 0 to A0.                                                                                          |

|   |   |     |    |                                                                                                                   |

### 6-Bit/8-Bit Color Selection

The command register bit B1 or the 6\*/8 pin can be used to specify whether the MPU is reading and writing 6 bits or 8 bits of color information each cycle. The 6/8 bit (bit B1 in Command Register B) and the 6\*/8 pin (pin #2) are logically ANDed. If the 6/8 bit is a logical one, the 6\*/8 pin controls 6- or 8-bit operation. While the 6/8 bit remains at logical zero, the MPU will read and write 6 bits of color information each cycle. For 8-bit operation, D[0] is the LSB and D[7] is the MSB of color data.

For 6-bit operation, color data is contained on the lower 6 bits of the data bus; D0 is the LSB, and D5 is the MSB of color data. When color data is written, D6 and D7 are ignored. During color read cycles, D6 and D7 will be a logical zero.

Accessing the cursor RAM array does not depend on the resolution of the DACs. If the 6\*/8 pin is held low (6-bit operation), the Bt481A will emulate a Bt471.

In the 6-bit mode, the Bt481A's full-scale output current will be about 1.5 percent lower than when in the 8-bit mode. This is because the 2 LSBs of each 8-bit DAC are always a logical zero when in the 6-bit mode.

#### **Power-Down Mode**

The Bt481A incorporates a power-down capability, controlled by the SLEEP command bit. While the SLEEP bit is a logical zero, the Bt481A functions normally.

While the SLEEP bit is a logical one, the DACs and power to the RAM are turned off. The RAM still retains the data. Also, the RAM may still be read or written to while the SLEEP bit is a logical one if the pixel clock is running. The RAM automatically powers up during MPU read/write cycles and shuts down when the MPU access is complete. The DACs will be turned off during sleep mode only if a voltage reference (internal or external) is used. If an external current reference is used, external circuitry should turn off the current reference (IREF = 0 mA) during sleep mode.

When an external voltage reference is used, external circuitry should turn off the voltage reference (VREF = 0 V) to further reduce power consumption caused by biasing of portions of the internal voltage reference.

### **SENSE\*** Output

SENSE\* is a logical zero if one or more of the IOR, IOG, and IOB outputs have exceeded the internal voltage reference level of the SENSE comparator circuit. This output determines the presence of a CRT monitor and, with diagnostic code, the difference between a loaded or unloaded RGB line can be discerned. The reference is generated by a voltage divider from the external 1.235 V voltage reference on the VREF pin. For proper operation of the SENSE circuit, the following levels should be applied to the comparator with the IOR, IOG, and IOB outputs:

DAC Low Voltage  $\leq 310 \text{ mV}$ DAC High Voltage  $\geq 430 \text{ mV}$

There is an additional  $\pm 10$  percent tolerance on the above levels when the internal voltage reference or an external current reference is used. SYNC\* should be a logical zero for SENSE\* to be stable.

### **Internal VREF and DAC Output Level**

When using the internal voltage reference of Bt481A, the DAC output levels are affected by the accuracy of the DACs as well as the voltage reference accuracy.

Figure 3 shows how the internal voltage reference interacts with the Bt481A DACs. At one input of the Bt481A op amp, a voltage reference of approximately 1.2 V exists. At the other input of the op amp, the value of the RSET resistor sets the full-scale current level for the DACs. The output of the op amp controls the IREF current source and in turn is fed back to the IREF pin.

Changing the voltage reference level or the value of the RSET resistor allows control of the IREF current level. The IREF current is mirrored by the DAC current cells which set the DAC output level (Iout).

The DAC output current level is determined by the following equation:

Iout = K \* VREF / RSET (See IREF pin description for K value.)

When using Bt481A's internal voltage reference, the variation in Iout for a given RSET is the result of variation in the internal voltage reference level as well as any error due to the DAC itself. Therefore, it is more meaningful to the user to focus on the overall Iout variation, rather than the individual variation of the internal voltage reference or the DACs.

1.2 V VAA VAA DAC Current Source

VREF IREF IREF Iout Vout Vout 37.5

Figure 3. Bt481A Internal VREF and DAC Output

### **Controller Interface**

The P[7:0] and OL[3:0] inputs are used to address the color palette RAM and overlay registers, as shown in Table 6. The contents of the pixel read mask register, which may be accessed by the MPU at any time, are bit-wise logically ANDed with the P[7:0] inputs. Bit D[0] of the pixel read mask register corresponds to pixel input P0. The contents of the overlay read mask register are bit-wise logically ANDed with the OL[3:0] inputs. Bit D[0] of the overlay read mask register corresponds to overlay input OL[0], and bit D[3] of the overlay read mask register corresponds to overlay input OL[3]. Bits D[7:4] of the overlay read mask register are ignored. Two consecutive write operations must be performed to write to the overlay read mask register. The first write is to the overlay read mask, and the second is to the pixel read mask. All 12 bits will be updated concurrently, synchronous to the pixel clock. Command Register B in the Internal Register section contains information regarding the accessibility of the overlay read mask register. The addressed locations provide 18 bits or 24 bits of color information to the three D/A converters.

The SYNC\* and BLANK\* inputs, also latched on the rising edge of CLOCK to maintain synchronization with the color data, add appropriately weighted currents to the analog outputs. This produces the specific output levels required for video applications, as illustrated in Figures 4–6. Tables 7–9 detail how the SYNC\* and BLANK\* inputs modify the output levels.

The SETUP input pin is logically ORed with the SETUP command bit and specifies whether a 0 or 7.5 IRE blanking pedestal is to be used.

The analog outputs of the Bt481A can directly drive a 37.5  $\Omega$  load, such as a doubly terminated 75  $\Omega$  coaxial cable.

Table 6. Pixel and Overlay Control Truth Table (Pixel Read Mask Register = \$FF)

| OL[3:0] | P[7:0] | Addressed by Pixel Port         |

|---------|--------|---------------------------------|

| \$0     | \$00   | Color Palette RAM Location \$00 |

| \$0     | \$01   | Color Palette RAM Location \$01 |

| :       | :      | :                               |

| \$0     | \$FF   | Color Palette RAM Location \$FF |

| \$1     | \$xx   | Overlay Color 1                 |

| :       | \$xx   | ·                               |

| \$F     | \$xx   | Overlay Color 15                |

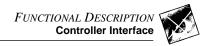

Figure 4. RS-343A Composite Video Output Waveforms (SETUP = 7.5 IRE)

Note:  $75 \Omega$  doubly terminated load; SETUP = 7.5 IRE. VREF = 1.235 V and RSET = 147  $\Omega$ . RS-343A levels and tolerances are assumed on all levels.

Table 7. RS-343A Video Output Truth Table (SETUP = 7.5 IRE)

| Description                                                                                         | Sync Disabled Sync Enabled |             | CVNC* | DI ANIZ* | DAC Innut Data |

|-----------------------------------------------------------------------------------------------------|----------------------------|-------------|-------|----------|----------------|

| Description                                                                                         | lout (mA)                  | lout (mA)   | SYNC* | BLANK*   | DAC Input Data |

| White                                                                                               | 19.05                      | 26.67       | 1     | 1        | \$FF           |

| Data                                                                                                | Data + 1.44                | Data + 9.05 | 1     | 1        | Data           |

| Data - Sync                                                                                         | Data + 1.44                | Data + 1.44 | 0     | 1        | Data           |

| Black                                                                                               | 1.44                       | 9.05        | 1     | 1        | \$00           |

| Black - Sync                                                                                        | 1.44                       | 1.44        | 0     | 1        | \$00           |

| Blank                                                                                               | 0                          | 7.62        | 1     | 0        | \$xx           |

| Sync                                                                                                | 0                          | 0           | 0     | 0        | \$xx           |

| Note: 75 $\Omega$ doubly terminated load; SETUP = 7.5 IRE. VREF = 1.235 V and RSET = 147 $\Omega$ . |                            |             |       |          |                |

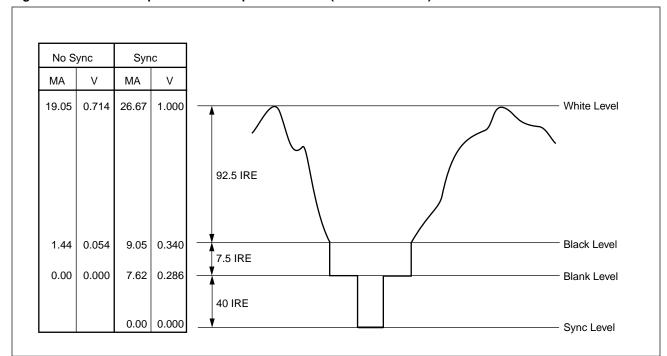

Figure 5. RS-343A Composite Video Output Waveforms (SETUP = 0 IRE)

Note: 75  $\Omega$  doubly terminated load; SETUP = 0 IRE. VREF = 1.235 V and RSET = 147  $\Omega$ . RS-343A levels and tolerances are assumed on all levels.

Table 8. RS-343A Video Output Truth Table (SETUP = 0 IRE)

| Description                                                                                       | Sync Disabled | Sync Enabled | SYNC* | BLANK* | DAC Input Data |

|---------------------------------------------------------------------------------------------------|---------------|--------------|-------|--------|----------------|

| Description                                                                                       | lout (mA)     | lout (mA)    | STNC  |        |                |

| White                                                                                             | 17.62         | 25.24        | 1     | 1      | \$FF           |

| Data                                                                                              | Data          | Data + 7.62  | 1     | 1      | Data           |

| Data - Sync                                                                                       | Data          | Data         | 0     | 1      | Data           |

| Black                                                                                             | 0             | 7.62         | 1     | 1      | \$00           |

| Black - Sync                                                                                      | 0             | 0            | 0     | 1      | \$00           |

| Blank                                                                                             | 0             | 7.62         | 1     | 0      | \$xx           |

| Sync                                                                                              | 0             | 0            | 0     | 0      | \$xx           |

| Note: 75 $\Omega$ doubly terminated load; SETUP = 0 IRE. VREF = 1.235 V and RSET = 147 $\Omega$ . |               |              |       |        |                |

16 L481A\_C Brooktree®

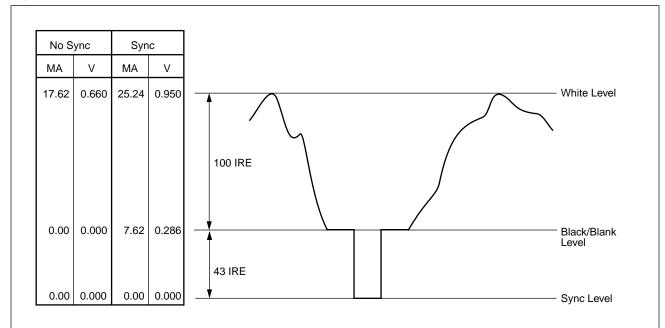

Figure 6. PS/2 Composite Video Output Waveforms (SETUP = 0 IRE)

Note:  $50~\Omega$  load (150  $\Omega$  DAC termination in parallel with 75  $\Omega$  monitor load); SETUP = 0 IRE. VRE = 1.235 V and RSET = 182  $\Omega$ . PS/2 levels and tolerances are assumed on all levels.

Table 9. PS/2 Video Output Truth Table (SETUP = 0 IRE)

| Description                                                                     | Sync Disabled | Sync Enabled | CVNC* | DI ANI/* | DAC Input Data |

|---------------------------------------------------------------------------------|---------------|--------------|-------|----------|----------------|

| Description                                                                     | lout (mA)     | lout (mA)    | SYNC* | BLANK*   |                |

| White                                                                           | 14.25         | 20.36        | 1     | 1        | \$FF           |

| Data                                                                            | Data          | data + 6.11  | 1     | 1        | Data           |

| Data - Sync                                                                     | Data          | Data         | 0     | 1        | Data           |

| Black                                                                           | 0             | 6.11         | 1     | 1        | \$00           |

| Black - Sync                                                                    | 0             | 0            | 0     | 1        | \$00           |

| Blank                                                                           | 0             | 6.11         | 1     | 0        | \$xx           |

| Sync                                                                            | 0             | 0            | 0     | 0        | \$xx           |

| Note: $50 \Omega$ load: SETUP = 0 IRE, VREF = 1.235 V and RSET = 182 $\Omega$ . |               |              |       |          |                |

**Brooktree**° 18 L481A\_C

### **Command Register A**

This register may be written to or read by the MPU at any time. All bits are initialized to logical zero on power-up. A logical one on bit A7 enables 15-, 16-, and 24/32-bit modes when used with bits A6, A5, and A4. If A7 is a logical zero, pseudo-color mode is enabled regardless of the state of A6, A5, or A4.

Bit A6 determines whether the device is in 15- or 16-bit-per-pixel mode.

Bit A5 determines whether the data is input on the rising edge of the input clock, or on the rising and falling edges of the input clock. A logical zero written to this bit indicates a dual-edge clock, and a logical one indicates a single-edge clock.

Bit A4 indicates a 24- or 32-bit input, i.e., a 24-bit true-color bypass only, or a 24-bit true-color bypass and an 8-bit VGA pass through. Bit A5 determines whether the pixels are input 8 bits at a time on every rising edge, or 8 bits at a time on rising and falling edges of the input clock. When bits A4 and A6 are set to logical one, the inputs are 24-bit true-color bypass, operating in single-edge clock mode.

| A7 | A6 | A5 | A4 |                                              |

|----|----|----|----|----------------------------------------------|

| 0  | х  | х  | х  | Pseudo Color (256 Colors)                    |

| 1  | 0  | 0  | 0  | 5:5:5 Dual-Edge Clock (33 K Colors)          |

| 1  | 1  | 0  | 0  | 5:6:5 Dual-Edge Clock (65 K Colors)          |

| 1  | 0  | 1  | 0  | 5:5:5 Single-Edge Clock (33 K Colors)        |

| 1  | 1  | 1  | 0  | 5:6:5 Single-Edge Clock (65 K Colors)        |

| 1  | 0  | 0  | 1  | 8:8:8 OL Dual-Edge Clock (16.8 M Colors)     |

| 1  | 1  | 1  | 1  | 8:8:8 Single-Edge Clock Only (16.8 M Colors) |

| A3 | Reserved (logical zero)                                                                                           | A logical zero must be written to this bit to ensure proper operation.                                                                                                                                                                                                                   |

|----|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2 | RS2 Select (0) RS2 signal controlled by RS[2] pin (1) RS2 signal controlled by A2                                 | If bit A2 in Command Register A is set to logical one, internally, the RS2 signal will also be set to logical one, even if the RS2 pin is grounded. If bit A2 in Command Register A is set to logical zero, the state of the RS2 signal will depend on the logic state of the RS[2] pin. |

| A1 | 24/32-Bit RGB or BGR Select (0) 24/32-bit RGB format selected (1) 24/32-bit BGR format selected                   | A logical zero written to this bit will set the 24- or 32-bit-per-pixel mode to RGB format. A logical one written to this bit will set the 24- or 32-bit-per-pixel mode to BGR format.                                                                                                   |

| A0 | Extended Register Select  (0) Extended register set cannot be accessed  (1) Extended register set can be accessed | A logical one written to this bit allows the user to indirectly access the extended register set. Included in the extended register set are Command Register B and Overlay Mask Register.                                                                                                |

### **Command Register B**

This register is operational only while bit A0 in Command Register A is a logical one. This register is initialized on power-up. On power-up, bits B7, B6, B5, and B0 are set to logical zero; bits B4, B3, B2, and B1 are set to logical one to enable the Bt481A to emulate the Bt478. While the 6\*/8 pin is held low, this register will be functionally ignored.

| B7 | Reserved (logical zero)                                                                            | A logical zero must be written to this bit to ensure proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |